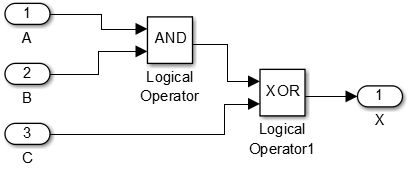

Para este primer ejemplo, generarémos el código VHDL para una función booleana sencilla de la forma X = AB xor C desde un diagrama en Simulink.

Bloques requeridos

HDL Coder > Commonly Used Blocks > In1

HDL Coder > Commonly Used Blocks > Out1

HDL Coder > Logic and Bit Operations > Logical Operators

Diagrama

Una vez terminado el bloque debemos irnos a la pestaña

Code > HDL Code > Generate HDL. Si no hay ningún error deberá aparecer lo siguiente en la ventana de comandos:

### Generating HDL for 'Ejemplo_HDL'.

### Starting HDL check.

### Begin VHDL Code Generation for 'Ejemplo_HDL'.

### Working on Ejemplo_HDL as hdlsrc\Ejemplo_HDL\Ejemplo_HDL.vhd.

### Creating HDL Code Generation Check Report Ejemplo_HDL_report.html

### HDL check for 'Ejemplo_HDL' complete with 0 errors, 3 warnings, and 0 messages.

### HDL code generation complete.

Por defecto el código generado aparecerá en el directorio hdlsrc\. El código generado para este ejemplo es el siguiente: